AMD 7nm Epyc 2 Rome could be a 9-Die Chip with New Socket

Rumors have been circulating for months surrounding the development of AMD’s next generation server processor, codenamed Rome. A new report has now emerged online claiming that the forthcoming Epyc 2 Rome chip will have nine dies with a total of 64 cores.

AMD’s 7nm Epyc – Expanding MCM even further

The second generation of Epyc processors is expected to land soon, in a few months. With Epyc 2, AMD not only relies on a 7nm process but also expands its multi-chip module (MCM) design further. MCM allows the company to interconnect several dies via an interconnect called Infinity Fabric, and operate as one large processor.

For example, AMD has used this design approach to interconnect dies with eight cores each to form Epyc and Threadripper processors with up to 32 cores. This approach is primarily cost effective as it is significantly cheaper to produce dies with only eight cores than a 28-core die from Intel.

Related: AMD 7nm Zen 2 will exceed Intel CPU performance: Canalys

On top of that, faulty or worse dies can be used in other lower-end products, thus increasing the production yield. This allows AMD to offer more affordable prices than Intel, making Epyc increasingly popular among consumers in the server division. Now the processors are ready to appear in the second generation and improve on the existing MCM approach.

Epyc 2 Rome comes with 9 Dies, Plus a New Socket

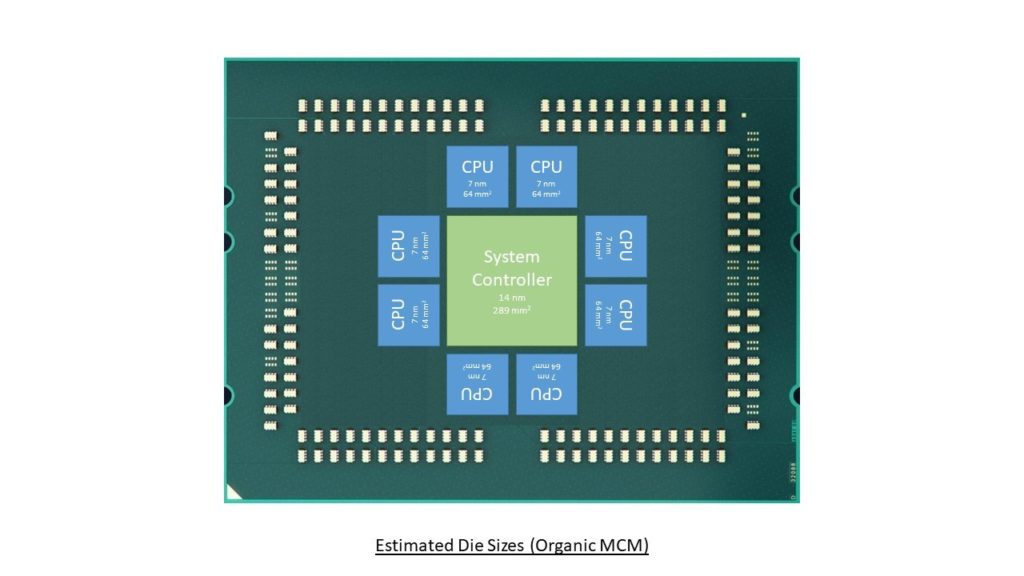

Built on the 7nm process node, the Epyc 2 processor dies shrink once again. Previous rumors suggest that AMD could have increased the number of cores in the dies from 8 to 16 in order to make 64-core processors. However, it seems that the manufacturer is going to take a different route.

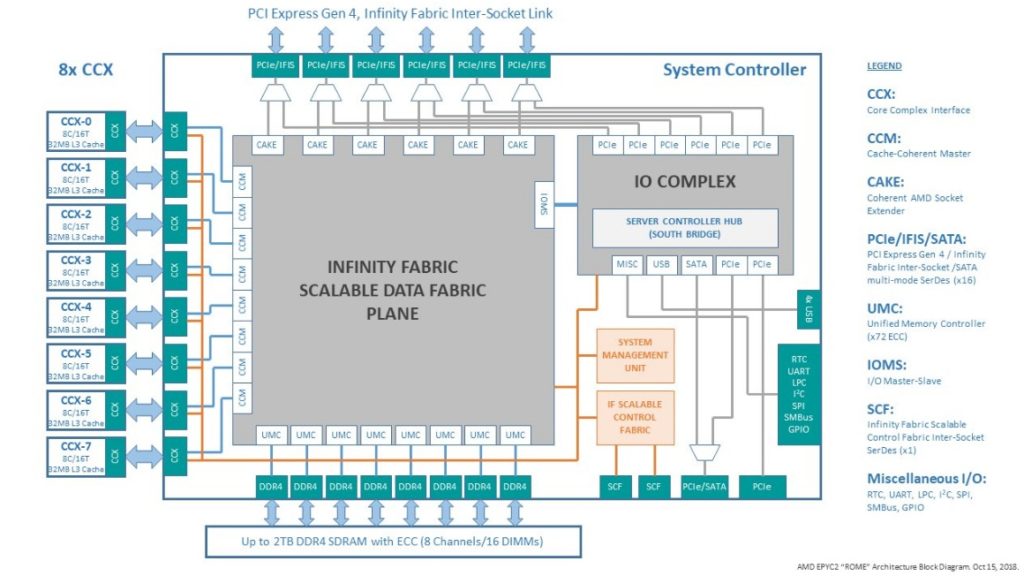

According to a report from SemiAccurate, the new Epyc 2 processors will not use any dies with 16 cores. Instead, they will opt for up to eight 7nm dies with eight processor cores each. There will also be a ninth chip, built on 14nm, that marks the evolution of the Infinity Fabric.

This ninth chip will be the central control element managing everything including the eight core dies, memory connectivity, I/O and caches. This means Rome will no longer rely on NUMA for RAM access; instead the latencies will be kept same for all dies, making workloads much faster than before.

The report also alleges that AMD’s Rome chip will feature a new socket. Normally, we get to see two generations per socket in the server area so Rome might seem like a deviation from the usual plan.

That’s because the first generation of Epyc, codenamed Naples, was supposed to be succeeded by a server CPU series called Starship with up to 48 cores. However, AMD has apparently decided to cancel Starship and move straight to Rome.

With the new socket, Rome should already support PCIe 4.0 offering 16 GB/s bandwidth. The even faster connection CCIX (25 GB/s), though, is reserved for the successor Milan, which should run on the same socket. Both Rome and Milan allegedly still use DDR4 memory, with DDR5 and 10-channel interface coming with the next-generation Genoa, which then gets a new socket.

We’ll hopefully get more information on Epyc 2 Rome in the next few days. AMD is set to hold an event in San Francisco soon, where it give update on the 7nm production and thus Rome and the new Vega graphics architecture, called Vega 20.